先前的研究表明,在FPGA或ASIC实现图像处理算法可以将CPU的能效提高500倍。随着主流计算向低功耗移动设备的发展,这种效率的提高变得越来越必要。来自图像处理和计算机视觉社区的最新研究不能作为软件在所述平台运行,因为它会消耗太多的电能或超过热极限。遗憾的是,大多数研究人员和公司都无法将最新的图像处理研究成果转化为定制硬件:硬件的设计和实现成本太高,开发时间太长。

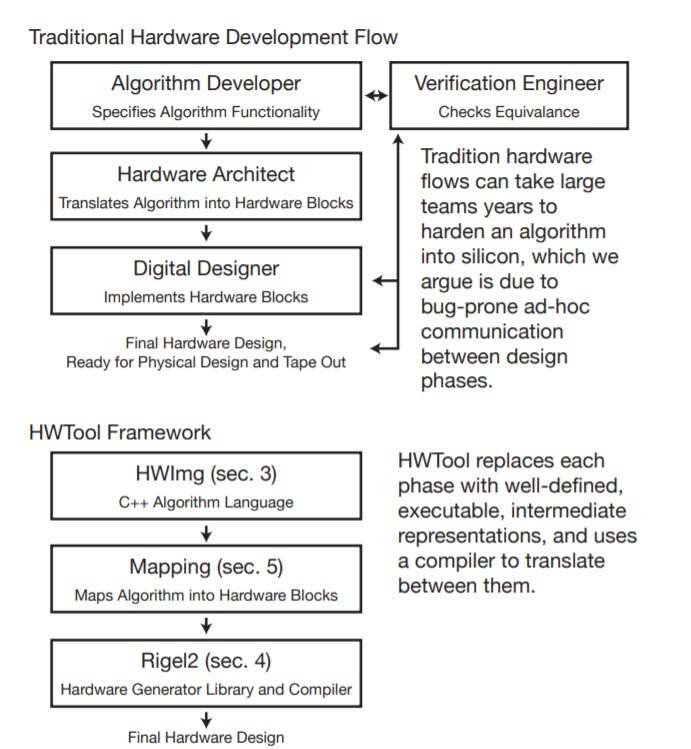

将最新的图像处理和计算机视觉研究引入到广泛的用户群要求我们降低定制硬件的成本和开发时间。硬件设计需要多次实现所需的算法,而每次都要满足开发过程的不同要求。首先,将算法作为高级软件实现,以证明相关方法能够解决期望的视觉或图像处理问题。接下来,硬件架构师将high level代码转换为精确指定的硬件块,并做出优化决策,例如选择较低的整数精度。

通常,这涉及实现精确硬件架构的软件模拟,以供参考和测试。最后,将所需的硬件架构再次实现为要合成的Verilog。所述手动实现和优化步骤中的每一个都是引入bug或错误通信的机会。另外,算法开发和硬件实现之间的长周期意味着可以发现优化机会。

鉴于改进的机会,硬件设计工具近年来已成为一个活跃的研究领域。研究人员已经提出了Verilog、C-to-gates High-Lelve Synthesis(HLS)工具的替代方案。不过,尽管所述工具有助于硬件设计过程中的各个阶段,但它们都没有帮助组织和优化从算法开发到最终硅的整个硬件流程。在所有这些工具中,硬件和软件开发团队之间的协调,以及支持下游验证工作依然是一个有待解决的问题。

在名为《HWTool: Fully Automatic Mapping of an Extensible C++ Image Processing Language to Hardware》的研究论文中,Meta和路易斯安那大学拉菲特分校介绍了一个可扩展的编译器和框架HWTool,以用于将图像处理和计算机视觉代码完全自动映射到定制硬件。

HWTool框架和编译器由多个Intermediate Representations(IRs)组成。HWTool的映射器在管道中的每个点查找每个HWImg操作符的本地最低成本硬件实现。对于HWTool的硬件后端,团队显著改进了Rigel以创建Rigel2。

作为说明,Rigel是一个简单的硬件IR和硬件生成器的标准库。硬件生成器通过一组固定的配置选项为每个操作符生成优化的Verilog。例如,Rigel的图像裁剪生成器将生成一个Verilog模块,从选定的图像大小裁剪选定数量的像素。Rigel2的IR允许编译器分析管道中每个中间层的吞吐量和接口要求,这有助于HWTool的映射器为每个操作符选择最佳的硬件实现。最后,研究人员展示了如何解决在RIGEL2中的FIFO缓冲器分配,从而实现了从C++到硬件的完全自动化的流程。

研究人员强调,这个项目的一个关键目标是创建一个可供硬件设计团队实际使用的工具。HWTool并不是为了取代硬件设计师,而是提供一个旨在帮助团队更有效地工作的框架。团队相信系统必须满足以下目标才能成功:

效率:只有在需要极高效率的情况下,在固定功能硬件中实现算法才有意义。硬件设计工具如果无法达到手动调整硬件的效率,则没有用处。

灵活性和可扩展性:Domain Specific Languages(DSL)可以公开方便的编程模型并执行令人印象深刻的优化,但它们通常功能有限,难以扩展。相反,团队必须提供一个灵活、可扩展的框架,并能够支持几乎所有可用Verilog等通用语言表达的硬件,同时允许以后添加功能。

互操作性:缓存、摄像头接口等常见硬件块很难实现和验证,大多数团队将使用所述组件的现有设计。系统必须能够利用现有设计,并作为现有硬件工具生态系统的一部分。

可控性:low-level生成硬件设计有时必须手动检查,例如,搜索bug或解决物理设计问题。编译器执行的映射很容易让人理解、调试和控制,这一点非常重要。这促使研究人员为编译器将执行的操作创建一个简单且定义良好的模型。

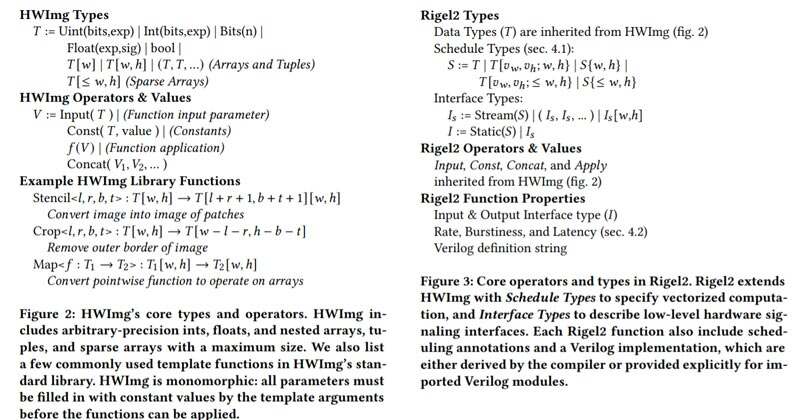

HWImg是HWoToice的C++图像处理语言前端。HWImg库是在以下约束条件下设计:

1.阵列或图像只能由完全并行的阵列运算符操作。不支持循环,这大大简化了依赖关系分析和下游编译任务。

2.HWImg设计成可扩展,并且很少有内置的操作符。几乎所有操作都是通过泛型函数调用执行的。开发者可以轻松添加新功能。

3.HWImg函数是单态函数:所有类型和数组大小都必须在编译时设置并保持不变。然而,类似于C++模板元编程,前端syntax sugar有能力自动填充所述参数。

接下来,HWTool必须将HWImg代码映射到Verilog中的硬件描述。为了实现这一点,团队将HWImg管道转换为Rigel2,这是一种可以编译为Verilog的新型硬件描述语言。对于从HWImg到Rigel2的映射,Rigel2包含对前面显示的Rigel语言的关键增强,它支持从高级语言自动映射。Rigel2的两个特性对于实现团队设定的目标至关重要。

首先,Rigel2可以在编译时可靠地内省每个信号的类型和运行时吞吐量,这允许自动专门化每个硬件实例,以便在需要它的站点中以最佳方式执行。其次,与HLS不同,Rigel2中的每个模块都直接映射到Verilog模块定义。这意味着可以轻松地将现有的Verilog模块导入到Rigel2管道中,从而实现与现有代码的互操作性。图3简要概述了Rigel2的类型和操作符。Rigel2与HWImg共享其核心数据类型和操作符,这使得编译语言的大部分内容变得微不足道。另外,Rigel2扩展了HWImg,添加了特定于硬件的注释。

最后,团队将HWImg中的high-level程序映射到Rigel2中的硬件管道。正如之前解释指出,映射并不简单:它必须正确地调整硬件的大小,以满足吞吐量要求,并适应硬件约束。HWImg中操作符的可靠组合要求一致地解决所述问题,否则配置、吞吐量和操作员的各种组合将无法映射。

尽管全局优化约束和吞吐量将带来最低的开销,但研究人员认为这将很难解决。相反,HWTool采取了一种方法:每个HWImg操作符在本地映射到一个硬件块,其中硬件块在管道中的该点满足或超过要求。

然后,研究人员只需要解决一个更简单的问题:允许组合具有不同(但兼容)接口的模块。图6指定了一组允许的类型、速率和向量宽度替换。其关键思想是,可以将更高吞吐量或更简单的接口转换为支持更低吞吐量或更复杂的接口。映射的第一步是遍历整个管道,并确定是否需要最为简单的static接口或更为复杂的stream接口。

在此之后,编译器再次遍历HWImg管道,并为每个操作符运行映射函数,返回满足或超过该站点吞吐量和速率要求的Rigel2模块实例。最后,映射的Rigel2模块之间的接口转换为匹配。

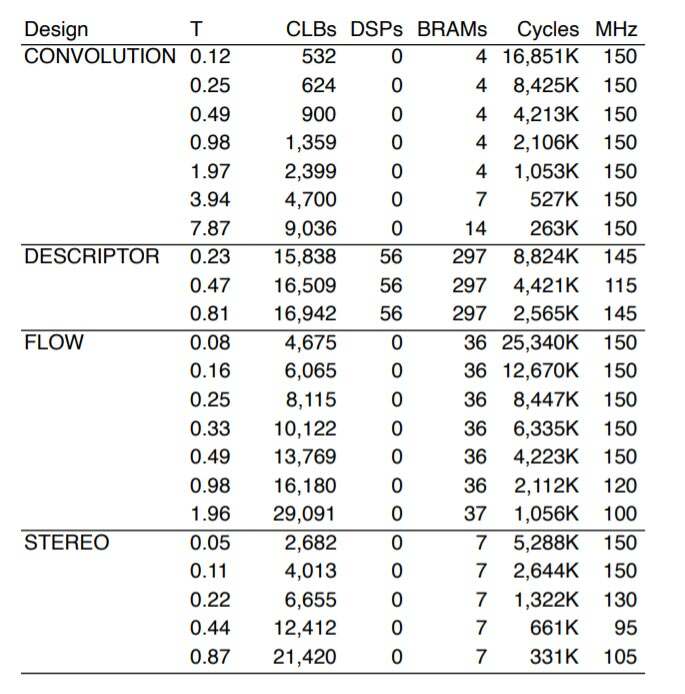

为了测试HWTool设计的正确性、范围和质量,研究人员在HWImg中实现了许多全尺寸图像处理管道,并使用HWTool将它们映射到硬件。然后,为Xilinx UltraScale+FPGA合成了硬件。

总的来说,所述研究的贡献主要包括:

1.提出了一种适合于非硬件专家算法开发者使用的higl level C++图像处理语言HWMG,并设计成令硬件映射问题易于处理。

2.提出了Rigel2。通过解决吞吐量和接口约束,这个硬件描述IR可以将HWImg映射到硬件。

3.演示了如何通过将每个操作符本地映射到最佳匹配的硬件模块,并在接口处插入任何必要的转换来将HWImg程序自动映射到Rigel2。

4.展示了如何在不需要注释的情况下将Rigel2映射到Verilog,方法是通过使用允许bursty模块的调度模块解决FIFO缓冲。

5.展示了所述贡献如何使HWTool自动将四个大规模图像处理管道映射到FPGA:卷积、立体深度、Lucas-Kanade光流和一个简单的特征描述符。最终的FPGA设计所使用的FPGA面积仅比手动优化设计多11%,比全自动FIFO分配多33%,与HLS的面积类似。

团队表示:“非常高兴HWTool可以为将算法映射到硬件的过程带来更多的结构、一致性和易用性。HWTool和硬件设计社区普遍面临的一个公开问题是缺乏高质量的开源硬件库。我们对这一领域的最新进展感到鼓舞,特别是在RISC-V方面。我们同时对我们的框架可能通过将困难的硬件映射问题分解为更小的可组合单元来实现的新研究感到兴奋。例如,我们的每个操作符、映射函数和Verilog模块都非常简单,每个接口和调度变量都可以从单个行为描述中自动合成并进行正式验证,而这在整个管道中非常困难。”

文章来源:映维网

评论